Key research themes

1. How can intermediate representations improve WCET flow analysis across diverse code formats?

Flow analysis to derive loop bounds, infeasible paths, and execution frequencies is key in static WCET analysis. However, varying code formats (source, intermediate, binary) complicate unified flow analyses. Research has investigated creating portable intermediate languages and representations to uniformly express code semantics, enabling reusable, precise flow analyses applicable across code formats to improve WCET estimation.

2. What methods exist to approximate or tighten WCET estimates through program structure and infeasible path exploitation?

Exact WCET calculation is challenged by infeasible paths and complex program structures that cause direct and indirect overestimations. Research has explored static analyses bounding loop iterations and detecting infeasible paths, as well as adding flow constraints or conflicts to WCET analyses. Advances include structural analysis, abstract interpretation for loop bounds, and integration of infeasible path information into the WCET computation via ILP and other constraint methods, reducing pessimism and increasing estimate tightness.

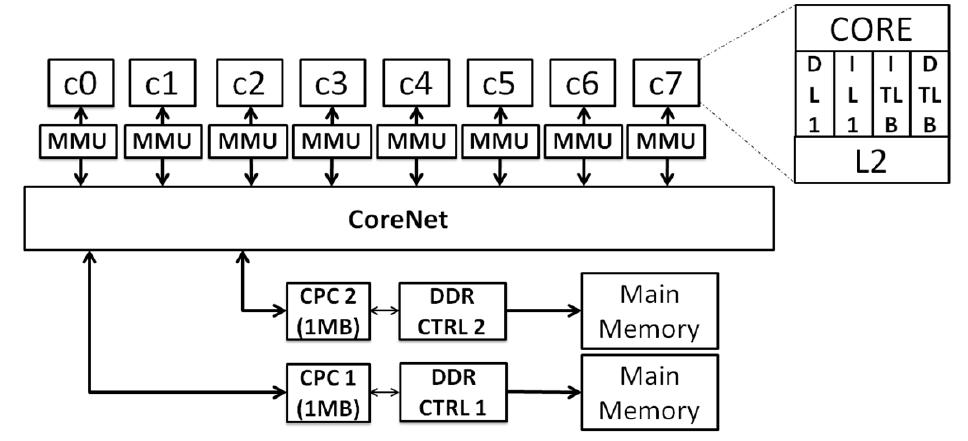

3. How can WCET analysis incorporate hardware resource contention and multi-core effects to obtain tighter, realistic execution time bounds?

With the rise of multi-core embedded platforms, shared hardware resource contention like caches, DRAM bandwidth, and bus arbitration significantly impacts WCET. Research explores modeling such contention via memory bandwidth regulation, budget assignments, and multicore-aware timing analyses. Novel analytical frameworks and run-time controls are proposed to mitigate contention-induced WCET overestimations and preserve real-time guarantees in shared resource environments.